Altair PollEx를 활용한 DDR 신호 무결성 분석 프레젠테이션을 소개합니다.

PollEx에서 신호 무결성(Signal Integrity) 시뮬레이션의 목적은 여러 요인을 분석하고 조정하여 최상의 신호 품질을 얻는 것입니다. 이 프레젠테이션에서는 솔루션을 소개하고 DDR 설계 적용 사례를 확인할 수 있습니다.

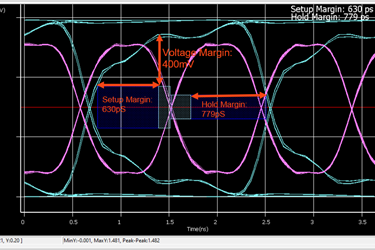

– 초기 개발 단계에서 적용된 Signal Integrity의 목적은 드라이버의 파형이 수신 단에 도달할 때 신호 왜곡을 예측하고 타이밍과 전압 margin을 확보하기 위함입니다.

– 임피던스의 부정합으로 인한 overshoot가 크며, IC의 수명이 단축되고 임계 영역을 침범할 때 시스템의 오작동을 일으킬 수 있는 큰 Ring-back을 생성하는 DDR 디자인 케이스를 제시하였습니다.

– 예측할 수 없고 예측 불가능한 요인들과 함께 시스템의 장애를 일으키지 않는 견고한 디자인을 가지도록 사전에 제어할 수 있는 요소의 충분한 설계 마진을 제공해야 합니다.

[개선방법 제안]

1. 임피던스 부정합으로 인한 overshoot을 감소시키기 위해 termination의 적절한 값 추가

2. reflection noise skew를 최소화하기 위한 Load 균형을 맞추기 위해 Topology를 조정

3. Crosstalk noise는 Ring-back을 악화시킬 수 있으므로, 가능한 한 crosstalk noise를 최소화

빠르고 신뢰할 수 있는 PollEx SI는 경쟁 관계이자 설립된 지 오래된 SI EDA 분석 소프트웨어와 동일한 수준의 정확도를 제공합니다.