프로세스 효율성은 잠재적인 결함을 식별하고 설계 단계에서 제조를 최적화하는 것으로 시작됩니다.

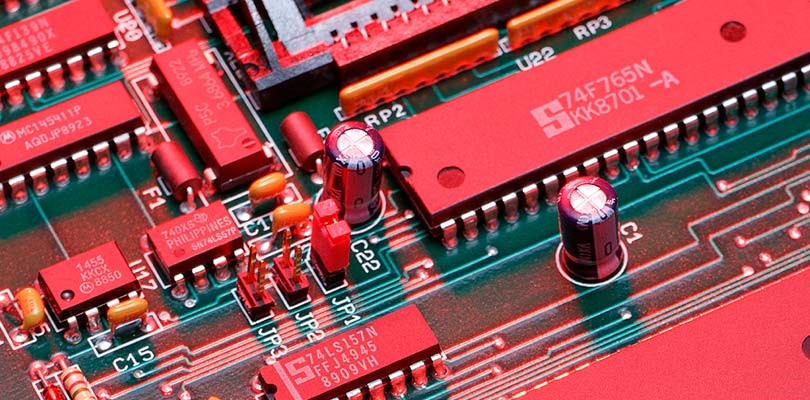

인쇄 회로 기판(PCB) 제조업체의 경우 신제품 소개(NPI:New Product Introduction)와 관련하여 가장 중요한 질문 중 하나는 “제조 프로세스의 품질과 일관성을 어떻게 보장하는가?”입니다.

결함이 발견되면 개발이 지연되고 비용이 많이 드는 재설계 및 테스트 사이클이 시작될 수 있으며, 혹시라도 이러한 결함 문제가 소비자에게 전달될 경우 제품 보증 비용이 증가하고 브랜드 평판에 큰 악영향을 미칠 수 있습니다

다음은 PCB 개발자들이 피하려고 하는 가장 일반적인 생산 이슈 5가지입니다.

1. Acid Traps

2. BGA 간격

3. 툼스톤(Tombstone) 효과

4. 테스트 포인트의 존재 여부

5. 비주얼(Visual) 특징

점점 더 많은 전자 제품 개발자들이 생산 효율성을 개선하고 PCB 생산을 방해하는 요인들을 피하기 위한 솔루션을 제공하기 위해 SDfM(Simulation-Driven Design for Manufacturing – 시뮬레이션 기반 제조용 설계) 방식으로 전환하고 있습니다.

어떻게 시뮬레이션으로 생산 효율성을 향상시킬 수 있나요?

PCB 개발 프로세스에 시뮬레이션을 적용하면 설계 엔지니어는 R&D 단계 초기에 제조 및 조립 문제가 다운스트림 검증 및 실 제품 테스트 단계에 도달하기 전에 잠재적 문제를 식별할 수 있습니다. SDfM은 일반적인 PCB 결함을 빠르고 정확하게 인식할 수 있는 광범위한 도구를 제공합니다. 그렇지 않을 경우 이를 발견하기 위해 광범위한 수동 검토나 Failed lab또는 필드 테스트를 필요로 하게 됩니다.

검증 검사는 제조 비용과 생산 주기를 줄이기 위해 필요한 단계입니다. 포괄적인 접근 방식에는 전기 유효성 검사(DFE, DFE+, LDFE)와 제조 유효성 검사(DFM, DFA)가 포함됩니다. 그러나 PCB 검증 도구만으로는 생산 효율성을 개선할 수 없습니다.

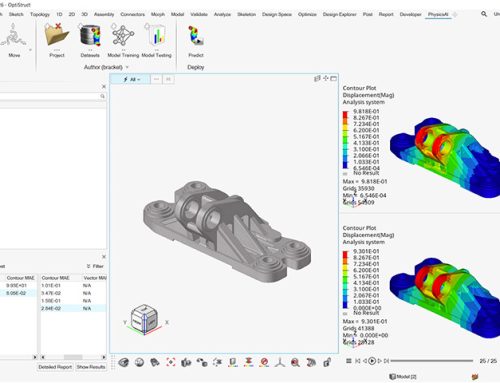

Altair PollEx는 오늘날의 스마트하게 연결된 전자 제품의 개발을 가속화하는 솔루션입니다. 전세계 유수의 기업들이 효율성을 개선하고, 성능을 높이고, 팀워크를 활성화하고, 협업을 강화하기 위해 사용하고 있는 이 제품은 기계, 열, 전자기 및 임베디드 코드 설계 흐름을 PCB 설계와 통합하는 전체 시스템 분석 도구를 제공합니다.

PollEx는 검증 테스트를 통해 생산 문제를 파악하는 것 외에도 제작, 조립, 테스트, Flex/Rigid-flex, 기판 및 패널 기능을 포함한 DFM/DFA 분석을 위한 솔루션을 제공합니다. 또한 PollEx는 제조, 조립 및 최종 테스트를 위해 제조 및 검증 데이터를 생산 라인의 기계로 내보냅니다. PollEx의 엔드 투 엔드 전자 시스템 개발 도구는 기능과 제조 가능성 모두에 대해 PCB 설계를 최적화하여 제조 비용과 생산 주기를 줄이는 데 도움이 됩니다.

일반적인 PCB 제조 문제를 방지하기 위한 유효성 검사

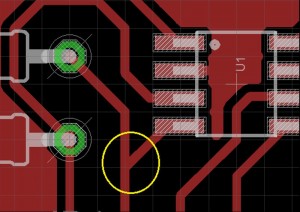

1. Acid Traps

Acid traps은 PCB의 포켓 공간으로, 일반적으로 날카로운 모서리로 에칭(etching) 용액이 들어갈 수 있습니다. 이러한 에칭 용액은 제조 과정에서 기판에 과도하게 구리를 제거하는 데 사용됩니다. 용액이 들어간 경우 보드를 통해 터널링되어 트레이스에 부식을 일으키고 트레이스가 결함을 일으킬 위험이 있습니다.

• 90도 이하의 트레이스 벤딩은 제조 중, 특히 트랩 영역에 잔류 산이 수집될 때 세척 전 Acid trap 역할을 할 가능성이 높습니다.

• Teardrops없이 Holes(Via 또는 DIP 연결부)에 연결된 트레이스는 일반적으로 예리한 각도로 연결되며, 이로 인해 Acid trap이 발생할 수 있습니다.

PollEx를 통한 검증

트레이스에 날카로운 모서리가 있는지 확인: 이 검사는 패드에 90도 각도로 연결된 패턴을 찾아 에칭 과정에 문제가 될 수 있는 경로를 사용자가 쉽게 수정하는 데 도움을 줍니다. 또한 사용자는 90도 각도로 패드에 들어오는 플래그가 지정된 모든 트레이스를 엿볼 수 있어 각도가 45도 또는 90도 이외의 각도로 라우팅 되는지 여부를 쉽게 확인하는데 도움이 됩니다.

Teardrops의 존재: 이 검사는 특히 Via들에 대한 브레이크아웃 가능성이 있는 DIP 유형 구성요소 그룹에 teardrops가 없는지 여부를 확인하는 데 도움이 됩니다.

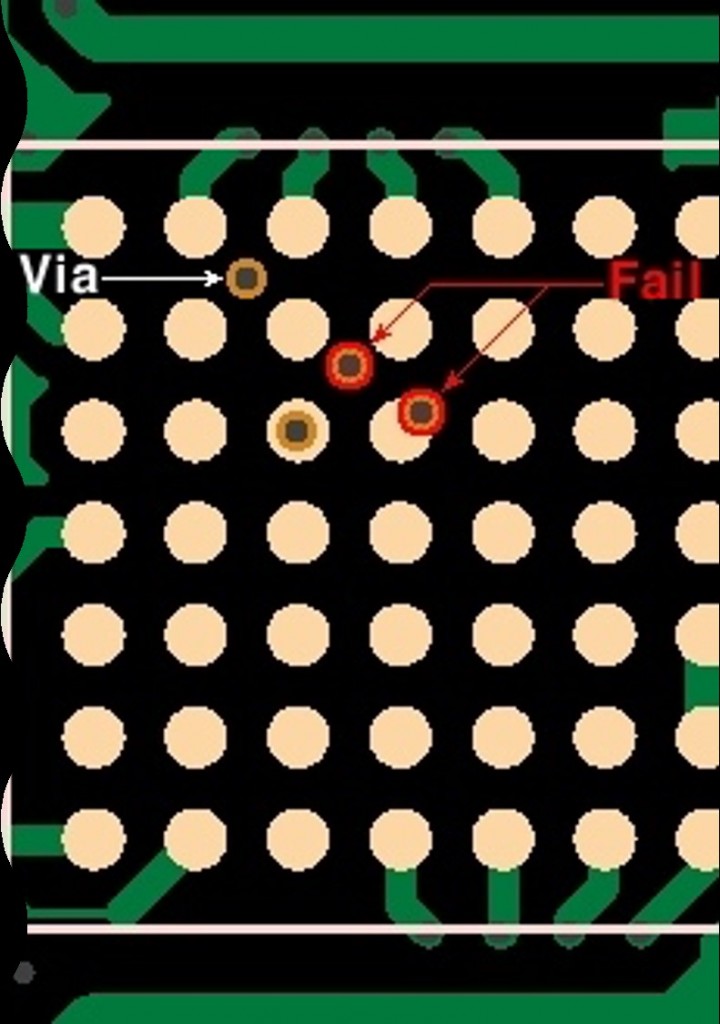

2. BGA Spacing

BGA 구성 요소는 고성능 IC를 집적도가 높고 복잡한 PCB에 통합하기 위한 주요 핵심요소입니다. 그러나 BGA 칩의 적절한 기능을 보장하기 위해 고려해야 할 몇 가지 문제가 있습니다. 제조 후 이러한 문제 중 일부를 수정하면 시간과 리소스 측면에서 비용이 많이 들 수 있습니다.

BGA 구성 요소는 고성능 IC를 집적도가 높고 복잡한 PCB에 통합하기 위한 주요 핵심요소입니다. 그러나 BGA 칩의 적절한 기능을 보장하기 위해 고려해야 할 몇 가지 문제가 있습니다. 제조 후 이러한 문제 중 일부를 수정하면 시간과 리소스 측면에서 비용이 많이 들 수 있습니다.

• BGA와 관련된 대부분의 문제는 다이(die) 아래의 볼 그리드용 패드와 관련이 있습니다.

• 각 BGA 패드 주변의 적절한 간격 설정을 통해 컴포넌트(부품)의 적절한 연결을 보장합니다.

PollEx를 통한 검증

Via에 대한 BGA 패드 주변의 클리어런스: 최선의 경우 BGA 라우팅을 위해서는 BGA 패드 사이의 through-hole via가 BGA 패드 4개의 중앙에 있어야 합니다. 그렇지 않을 경우 대부분의 BGA 패드가 비솔더(non-solder) 마스크로 정의되므로, (솔더 마스크 영역이 메탈 패드 면적보다 큼) BGA 패드에 도포된 솔더가 Via를 통해 빠져나갈 수 있습니다.

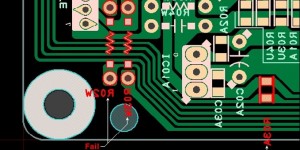

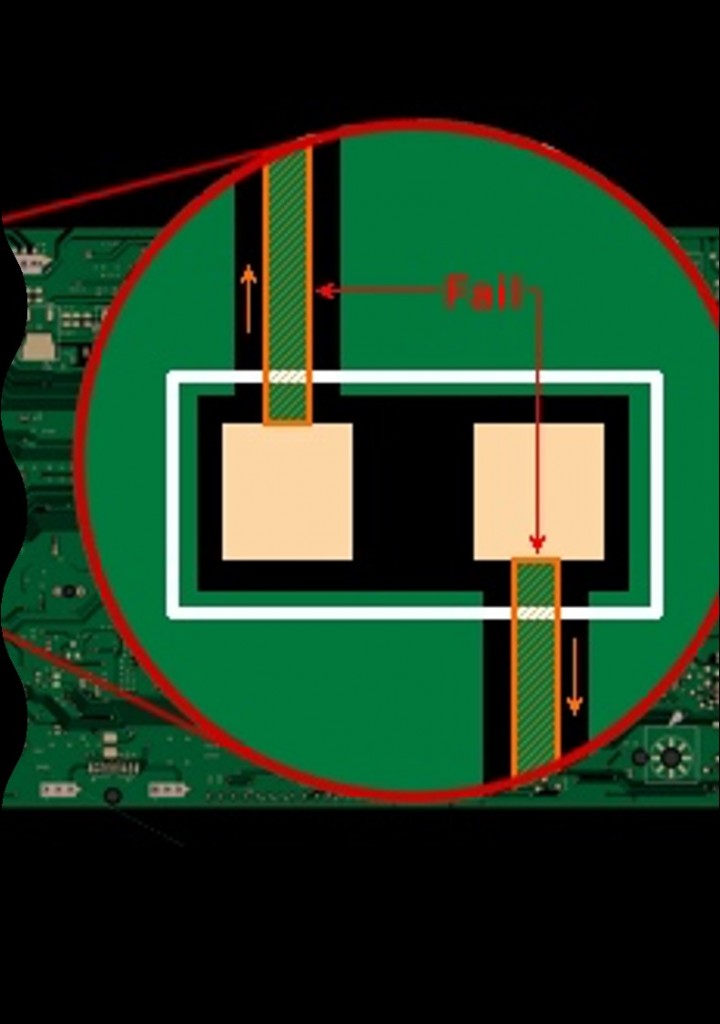

3. 툼스톤(Tombstone) 효과

툼스톤은 부적절한 습식으로 인해 발생합니다. 솔더 페이스트가 녹기 시작하면 부품 단자 끝에서 불균형한 토크가 부품의 한쪽 끝을 들어 올립니다.

• 2핀 장치의 각 패드에 연결된 트레이스가 서로 다르면, 리플로잉 프로세스 중에 납땜 시간이 달라져 부품이 툼스톤 됩니다.

PollEx를 통한 검증

연결된 트레이스의 비율 비교: 두 패드 사이의 열 분산 트레이스가 일치하지 않기 때문에, 하나의 패드가 제대로 연결되려면 더 많은 열이 필요할 수 있습니다. 따라서 온도 차이로 인한 습윤력 뷸균형이 발생하여 툼스토닝(tombstoning)이 발생됩니다. 툼스토닝을 방지하려면 패드에서 연결된 구리 사이의 비율이 허용가능한 비율 이내에 있는지 확인해야 합니다.

4. 테스트 포인트의 존재 여부

테스트 포인트는 회로의 상태를 모니터링하거나 테스트 신호를 주입하는데 사용되는 전자 회로 내의 위치입니다. PCB를 설계할 때 중요한 네트 및 부품을 쉽게 테스트할 수 있도록 고정 장치를 추가하는 것이 중요합니다.

테스트 포인트는 회로의 상태를 모니터링하거나 테스트 신호를 주입하는데 사용되는 전자 회로 내의 위치입니다. PCB를 설계할 때 중요한 네트 및 부품을 쉽게 테스트할 수 있도록 고정 장치를 추가하는 것이 중요합니다.

이러한 테스트 설정은 설계를 수정하거나 재작업 없이 Object를 테스트하는 데 필수적입니다.

• 설계 단계에서 테스트 포인트를 간과할 경우 제조 및 조립 단계에서 확인 중에 장비 오류를 진단하기 어려울 수 있습니다.

PollEx를 통한 검증

테스트 포인트 확인: 일반적으로 테스트 포인트는 전원 공급 또는 접근이 어려운 중요한 넷과 부품을 테스트하기 위한 디자인에 포함되지만 일부 영역은 누락될 수 있습니다. PollEx는 지정된 부품 및 네트에 대한 테스트 포인트의 존재 여부를 확인합니다.

제조 가능한 PCB를 설계할 때 오버레이 레이어는 제조 공정과 제조 후 디버그에서 중요한 역할을 합니다. 오버레이 레이어에는 첫 번째 핀 마크, 레퍼런스 이름 및 컴포넌트 아웃라인과 같은 정보를 포함합니다. 레이아웃 불일치를 방지하려면 이러한 오버레이 레이어에 대한 정보가 정확하게 표시되도록 하는 것이 중요합니다.

• 복잡한 다중 행 핀 IC의 경우 첫 번째 핀 표시는 배치할 때 디버깅에도 도움이 됩니다.

• 패시브 구성 요소 배열의 경우, 레퍼런스 이름은 회로도와의 크로스프로빙에 대한 세부 정보도 제공합니다.

• 이러한 레퍼런스 이름은 패드 및 Via와 같은 구리 영역 위나 컴포넌트 아래에 배치해서는 안됩니다.

PollEx를 통한 검증

– 배열된 패시브 컴포넌트의 레퍼런스 이름 순서 확인: 배열된 컴포넌트의 레퍼런스 이름 순서는 어레이에 배치할 올바른 컴포넌트와 연관되도록 정확해야 합니다.

– 복잡한 IC(레퍼런스 이름이 “U#”인 컴포넌트)에 대한 첫 번째 핀 마크가 있는지 확인: 복잡한 IC에 대한 첫 번째 핀을 표시하면 조립 프로세스 중에 컴포넌트가 잘못된 방향으로 배치될 수 있는 오류를 방지하는 데 도움이 됩니다.

– 다른 오브젝트(컴포넌트, 패드 및 홀)와 겹치는 레퍼런스 이름 확인: 홀 속의 잉크나 트레이스 위에 잉크가 있어 SI, PI에 문제가 발생하거나, 납땜이 가능한 표면에 잉크, 불량 솔더 조인트를 생성하는 것과 같은 다양한 문제가 발생하는 것을 방지하려면, 보드의 특정 오브젝트에 레퍼런스 이름이 겹치지 않도록 해야 합니다.

검증 결과 공유

제조 검증 테스트 결과를 효과적으로 배포하는 것은 중요한 점검을 직접 수행하는 것만큼 중요합니다. PollEx DFx는 이러한 검사의 모든 정보가 원활하게 배포되도록 하는 고유한 Export 기능을 제공합니다. 사용자 지정 Excel 서식을 통해 주변 팀과 상세한 정보를 공유하고 Export 할 수 있습니다.

알테어의 시뮬레이션 중심 설계 도구를 사용하면 전문 엔지니어 팀이 개념에서 제조에 이르는 인쇄 회로 기판 개발의 모든 측면에서 협업을 수행할 수 있습니다. 여기를 클릭하면 알테어 제품이 프로세스를 간소화하고, 설계의 반복을 줄이며, 출시 시간을 단축하는 방법을 알아보실 수 있습니다.

PCB 제조를 최적화하는 방법에 대해 자세히 알고 싶으신가요? 알테어와 IEEE에서 주최하는 웨비나에서 확인하세요.

감사합니다.

한국알테어