RAM(Random Access Memory)은 모든 전자 장치의 중심 구성 요소입니다. RAM은 데이터와 명령을 전자적으로 저장하여 장치가 기본 기능을 수행할 수 있도록 합니다. 디지털 데이터 스토리지 방법의 개선은 끊임없이 증가하는 전자 제품 혁신 속도와 긴밀히 연관되어 있습니다. 향상된 메모리 인터페이스 방법의 도움으로 PCB 디자이너와 엔지니어는 우리가 매일 사용하는 스마트 장치의 성능과 처리 속도를 높이는 데 큰 도약을 이루었습니다.

DDRx란 무엇일까요?

DDR(Double Data Rate) SDRAM(Synchronous Dynamic Random Access Memory)은 대부분의 최신 프로세서에서 RAM으로 사용되는 일반적인 유형의 메모리입니다. 1990년대에 처음 도입된 이 고성능 저비용 메모리 솔루션은 개인용 컴퓨터와 기타 가전 제품을 대상으로 했지만 그래픽, 네트워킹, 서버 및 기타 애플리케이션에서도 채택이 증가하고 있습니다. 시계와 데이터가 모두 소스에서 발생하는 소스 동기식 스위칭에서 소스와 타깃 모두에서 데이터가 동기화되는 보다 역동적인 방식으로 전자 장치를 전환하는 원동력이었습니다. 이를 통해 시계는 데이터와 함께 이동하다가 결국 데이터 내부에 숨겨져 데이터 정밀도를 높이고 시계 주파수를 줄임으로써 회로 기판의 신호 무결성 요구 사항을 줄일 수 있었습니다. DDRx는 DDR 메모리의 최신 버전으로, 원래 세대의 DDR에 비해 대역폭이 16배 이상 증가했습니다.

요즘은 제품 비용을 경쟁력 있게 유지하면서 원하는 성능을 제공하기 위해 고속 DDRx 메모리 인터페이스를 필요로 하는 스마트 커넥티드 기기가 늘고 있습니다. 메모리 회로 설계는 항상 주의가 필요하지만 DDR 메모리용 PCB 레이아웃은 더 까다롭습니다. 특히 최신 DDRx 메모리 인터페이스 표준의 경우, 기존의 규칙 기반 접근 방식으로는 충분하지 않은 경우가 많습니다. 시행착오 접근 방식을 버리고 전자 제품 개발자들은 장치의 메모리 인터페이스의 신뢰성과 견고성을 보장하기 위해 가상 설계, 시뮬레이션 및 검증 도구로 눈을 돌리고 있습니다.

Samsung SDI 및 기타 주요 제조업체에서 사용하는 Altair PollEx는 DDRx 타이밍, 전송 라인, 토폴로지 및 터미네이션을 최적화하여 신호 무결성(SI)을 보장하고 초기 설계를 용이하게 합니다.

DDRx를 처음부터 올바르게 설계하기

DDR 인터페이스는 소비재, 자동차, 통신, 의료, 산업 자동화 등과 같은 산업 전반의 전자 제품 응용 분야에 널리 사용되는 유비쿼터스이지만, 각 DDR 설계는 매우 독특하여 개별적인 주의와 관리가 필요합니다. 현 세대의 DDR 인터페이스와 관련하여 시뮬레이션 기반 설계 소프트웨어를 개발 프로세스에 있어서 점점 더 중요하게 만드는 몇 가지 설계 과제가 있습니다.

한 가지 문제는 시간이 지남에 따라 메모리 인터페이스에 공급되는 전압 범위가 감소한다는 것입니다. 2000년에는 2.5~2.6V 범위에서 사용 가능한 공급 전압을 기대할 수 있었지만, 2020년대에는 설계자가 1.1V만 사용할 수 있는 경우가 많습니다. 설계자는 전압 제한으로 인해 PCB의 설계, 제조 및 조립에 정밀도가 요구되므로 오류에 대한 여유를 더 좁혀야 합니다.

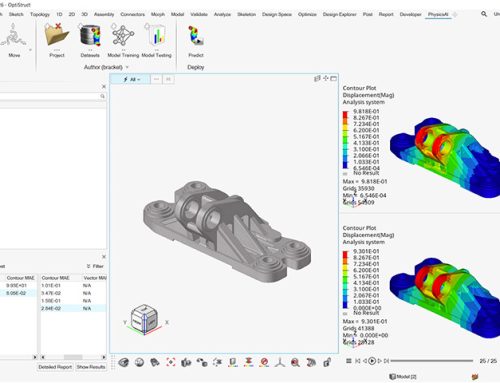

PCB 설계의 전기적 유효성 검사를 위한 Altair PollEx 기능 선택

또한 강력한 인터페이스를 만들기 위해 조정해야 하는 광범위한 정성적 및 정량적 측정 기준이 있습니다. 여기에는 타이밍 관계, SI 및 타이밍 파라미터, 임피던스, 길이 일치, 커플링 및 크로스토크와 같은 검증 및 구동 강도 및 슬루 레이트 지속과 같은 기타 파라미터가 포함됩니다.

DDR 개발의 가장 큰 걸림돌은 아마도 전통적인 설계 방식 그 자체일 것입니다. 일반적으로 기업들은 인터페이스당 3회 이상의 DDR 설계 반복을 거치며, 반복당 2-3시간 정도의 인력을 소모합니다. 개발 프로세스 전반에 걸쳐 설계자와 엔지니어는 반사, 왜곡, XT 또는 SSN과 같은 중복되는 문제에 직면할 수 있으며, 이는 커뮤니케이션 및 프로세스의 비효율성을 초래할 수 있습니다. 그런 다음 기존의 접근 방식에서는 피상적인 분석만 수행되는데, 이는 실패의 근본 원인을 놓치고 검증 적용 범위를 주요한 네트로만 제한하여 더 이상의 최적화 기회를 탐색하기 어렵습니다.

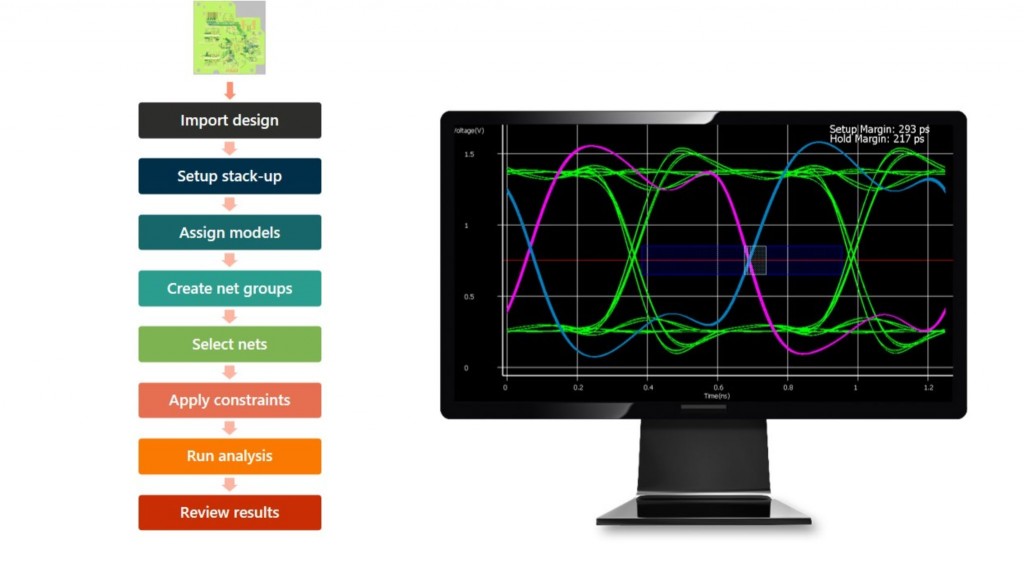

기존 PCB 설계 방식과 시뮬레이션 기반 PCB 설계 방식 비교

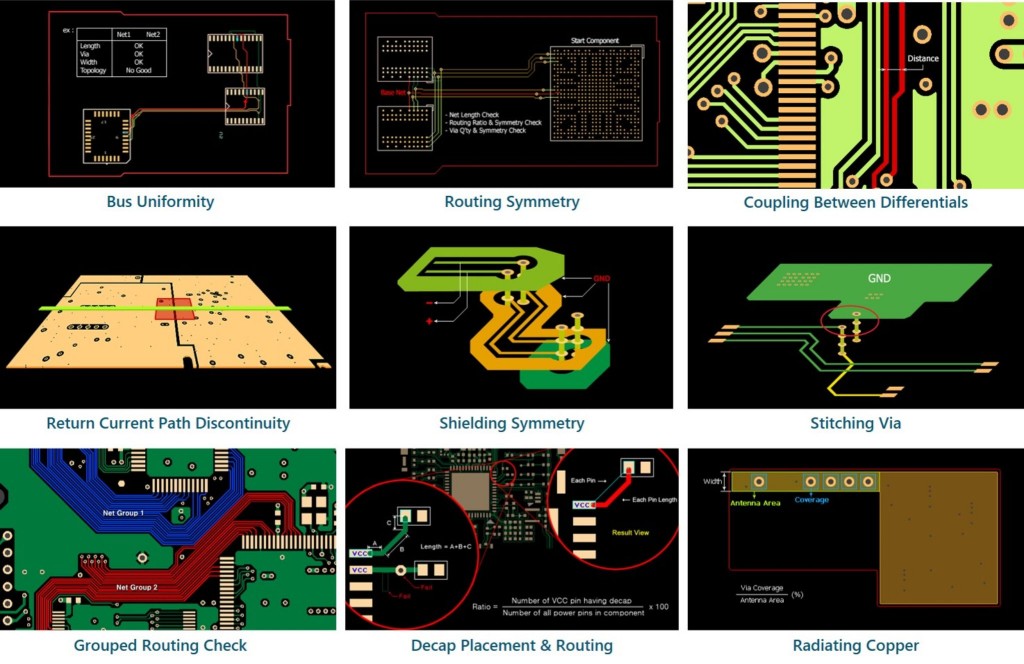

알테어의 시뮬레이션 기반 설계 프로세스는 3단계 깔때기 방식을 사용하여 더 빠른 개발을 가능하게 합니다. 먼저, PollEx DFE를 사용한 고급 기하학적 검증이 수행되며, 일반적으로 반복당 5분밖에 걸리지 않습니다. 그 다음에는 PollEx DFE+로 고급 전기 검증을 활용하여 대략적인 분석 단계를 거칩니다. 이는 기하학적 검증과 함께 설계자가 최종 미세 분석 단계 이전에 공정 초기의 잠재적인 PCB 설계 결함을 발견하고 수정하는 데 도움이 됩니다. 세 번째 단계인 PollEx SI를 사용한 DDR 시뮬레이션은 설계가 초기 검증 및 분석 검사를 통과한 후 PCB의 성능을 자세히 보여줍니다. 이 방법론은 PCB 설계자가 DFEx 규칙을 사용하여 문제를 보다 쉽게 식별하고 격리하며 다운스트림 분석 및 테스트 단계에서 비용과 시간이 많이 소요되는 오류 사례를 줄일 수 있도록 지원합니다.

Altair PollEx의 신호 무결성 DDRx 시뮬레이션 워크플로우

설계 반복 횟수를 줄이면 많은 전자 제품 제조업체의 운영 규모를 고려할 때 순이익에 큰 영향을 미칠 수 있습니다. 삼성SDI는 설계 반복 횟수를 20회에서 9회로 줄이고 수정 점검 횟수를 6회에서 3회로 줄인 덕분에 연간 600만 달러가 절감될 것으로 예상하고 있습니다.

Altair PollEx를 사용한 DDRx 설계에 대해 자세히 알아보려면 아래 링크를 클릭하여 최근 웨비나를 확인해보세요! 소프트웨어 데모를 포함하여 프로세스에 대한 자세한 설명을 확인할 수 있습니다.

원문은 (여기)에서 확인하실 수 있습니다.

감사합니다.

한국알테어